Advanced Information Version 1.0

Nov 12, 2006

# **T118B Video Display Controller**

# **Table of Contents**

| 1 | IN         | TRODUCTION                                                                      | .3  |

|---|------------|---------------------------------------------------------------------------------|-----|

|   | 1.1        | FEATURES                                                                        | . 3 |

|   | 1.2        | GENERAL DESCRIPTION                                                             |     |

|   | 1.3        | APPLICATIONS                                                                    |     |

|   | 1.4        | System Architecture                                                             |     |

|   | 1.5        | SYSTEM CONFIGURATIONS                                                           |     |

|   | 1.6<br>1.7 | PINOUT DIAGRAM                                                                  |     |

|   |            | IEORY OF OPERATIONS                                                             |     |

| 2 | IH         |                                                                                 |     |

|   | 2.1        | I <sup>2</sup> C COMMAND PROTOCOL                                               |     |

| _ | 2.2        | ANALOG FRONT END                                                                |     |

| _ | 2.3        | Y/C SEPARATION AND CHROMA DECODER<br>DIGITAL COLOR TRANSIENT IMPROVEMENT (DCTI) |     |

| _ | 2.4<br>2.5 | DIGITAL COLOR TRANSIENT IMPROVEMENT (DCTT)                                      |     |

|   | 2.6        | FIR SCALER                                                                      |     |

| - | 2.7        | BLACK-LEVEL EXTENSION (BLE)                                                     |     |

|   | 2.8        | COLOR SPACE CONVERTER                                                           |     |

| 2 | 2.9        | GAMMA CORRECTION                                                                | 17  |

|   | 2.10       | OSD                                                                             |     |

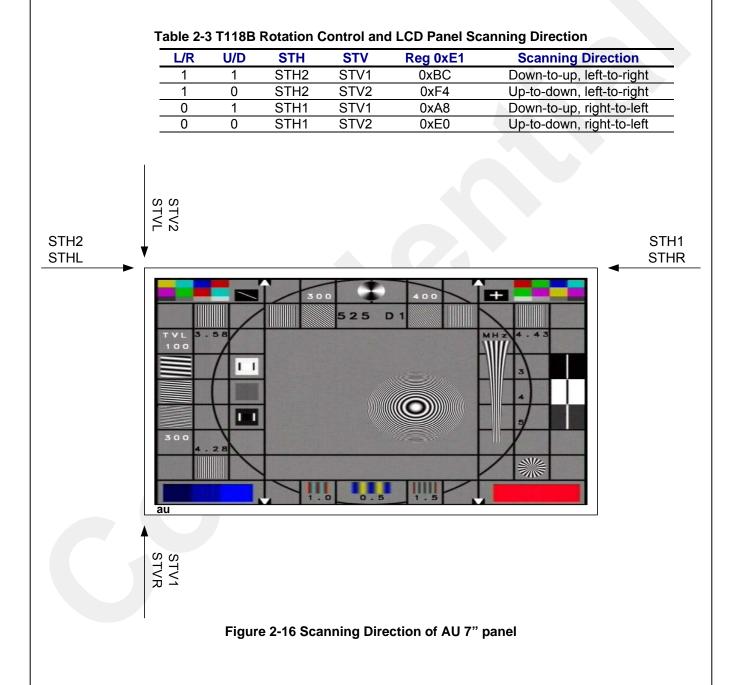

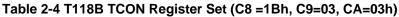

| 2 | 2.11       | TCON                                                                            | 30  |

| 3 | RE         | GISTER DESCRIPTION                                                              | 33  |

|   | 3.1        | ADC REGISTER SET                                                                | 33  |

|   | 3.2        | PICTURE ENHANCEMENT REGISTER SET                                                |     |

| 2 | 3.3        | SCALING REGISTER SET                                                            | 46  |

| 2 | 3.4        | COLOR SPACE CONVERTER REGISTER SET                                              |     |

|   | 3.5        | OSD REGISTER SET                                                                |     |

| - | 3.6        | LCD OUTPUT CONTROL REGISTER SET                                                 |     |

|   | 3.7        | TCON REGISTER SET<br>Y/C SEPARATION AND CHROMA DECODER REGISTER SET             |     |

|   | 3.8        |                                                                                 |     |

| 4 | EL         | ECTRICAL CHARACTERISTICS                                                        | 83  |

| 2 | 4.1        | DIGITAL I/O PAD OPERATION CONDITION                                             | 83  |

|   | 4.2        | AC CHARACTERISTICS                                                              |     |

|   | 4.3        | ANALOG PROCESSING AND A/D CONVERTERS                                            |     |

| 2 | 4.4        | ABSOLUTE MAXIMUM RATING                                                         | 84  |

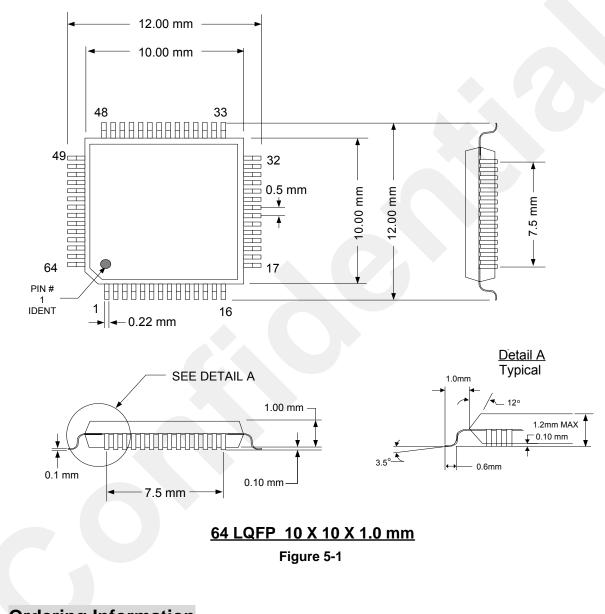

| 5 | PA         | CKAGE DIMENSIONS                                                                | 85  |

| 6 | OF         | RDERING INFORMATION                                                             | 85  |

|   |            |                                                                                 |     |

| 7 | RF         | VISIONS NOTE                                                                    | 86  |

| 8 | GE         | ENERAL DISCLAIMER                                                               | 86  |

| 9 | CC         | ONTACT INFORMATION                                                              | 86  |

| - | 20         |                                                                                 | 20  |

### 1 Introduction

#### 1.1 Features

#### Cost Effective Highly Integrated Triple ADC + + 2D Video Decoder + OSD + Scaler + TCON

- Integrates 9-bit Analog to Digital Converters (ADC) & Phase Locked Loop (PLL)

- Scaler supports 2-D adaptive intra-field deinterlacer and non-linear 16:9 aspect ratio.

- Requires no external Frame Buffer Memory for deinterlacer.

- Advanced On Screen Display (OSD) function

- Programmable Timing Controller (Tcon) for Car TV applications

- Multi-standard color decoder with 2D adaptive comb filter

- Innovative and flexible design to reduce total system cost

#### Triple 9-bit Analog to Digital Converters (ADC)

#### 27 MSPS Conversion Rate

- Built-in Pre-amp, mid-level & ground clamp circuit

- Automatic Clamp Control for CVBS, Y/C and YPbPr

- Programmable Static Gain Control or Automatic Gain Control for CVBS ,Y/C or YPbPr

- Max Input configuration up to 6xCVBS, 2xSvideo and 2xCVBS or 1xCVBS, 1xS-Video and 1xYPbPr

#### Digital Video Enhancement

#### Separate Luminance and Chroma Enhancer

- Y Supports Luminance Peaking, DLTI, Black Level Expansion, Contrast and Brightness adjustment

- C Supports DCTI, Saturation and Hue adjustment.

#### Advanced Scaling Engine

#### Two Dimensions FIR Scaler

- Coefficient based sharpness filters

- 2-D edge enhancement

- Independent vertical and horizontal scaling ratio

- 16:9 Non-linear Aspect ratio

- Cell-based scaling to detail horizontal image pixels

#### LCD Interface

- Provides 256-entry TBL Gamma correction for panel compensation

- Supports image pan functions

- Programmable Timing Controller

- Built-in software adjustable VCOM voltage

- 5.0v RGB Triple DAC output or Digital Serial RGB

- Integrated high efficiency DC-DC power conversion unit for gate and source drivers reduces energy consumption

- Integrated LCD backlight inverter drive unit supports LED typed backlight

- Software adjustable lamp dimming

#### Color Management

- Coef Programmable YCbCr-to-RGB Color Space Converter

- Independent RGB Gamma Correction

- Built-in On Screen Display Engine

- 3K-word OSD SRAM memory

- 1K-word Built-in font ROM

- Supports font or bitmap modes

- Supports character blinking, overlay, shadow and border functions

- Fully programmable character mapping

- Supports alpha blending & Zoom-in/Zoomout function

- Optional fonts can be stored in off-chip serial EEPROM

#### Versatile VBI Data Decoder

- Supports Close Caption, Wide Screen Signalling and Teletext

#### Crystal Oscillator Circuit

- Direct interface to a (27.0MHz or other frequency) Crystal

- Also provide a buffered clock output for external Micro-controller

#### Digital Test Pattern Generator

- Programmable standard & special panel burn-in test patterns

- Support special border frame blocking mode

#### Independent Display Phase Lock Loop

- Generates pixel clock output to panel

- Supports free run OSD mode

- Spread spectrum clock

#### Serial Bus Interface

- Supports 2-wire (normal speed)

#### Pulse Width Modulation Outputs

- Design For Testability

- Scan chain insertion

- Separated analog & digital test modes

- Power Supply: +1.8V & +3.3V

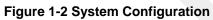

- Package: 64-pin LQFP

### 1.2 General Description

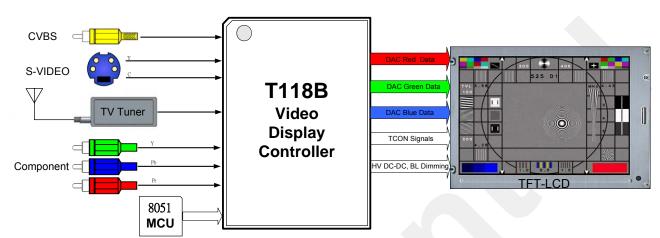

The T118B is a highly integrated All-in-one Visual Processor that provides major cost saving solution for the portable applications. T118B has built-in high performance dual ADCs (support YCbCr), TCON, Triple DACs, Scaling Machine with sophisticated upscaling and downscaling algorithms. The Innovative integrated "Frame-Buffer-Less" Deinterlacer can significantly reduce system cost. The T118B also integrates On Screen Display engine with 3K-words of font RAM and built-in 1K-words of font ROM. The device can interface to an external microcontroller through 2-wire serial bus interface.

### 1.3 Applications

- 1. 1.8-inch to 10-inch portable DVD or in-car TV

- 2. Progressive CRT TV

### 1.4 System Architecture

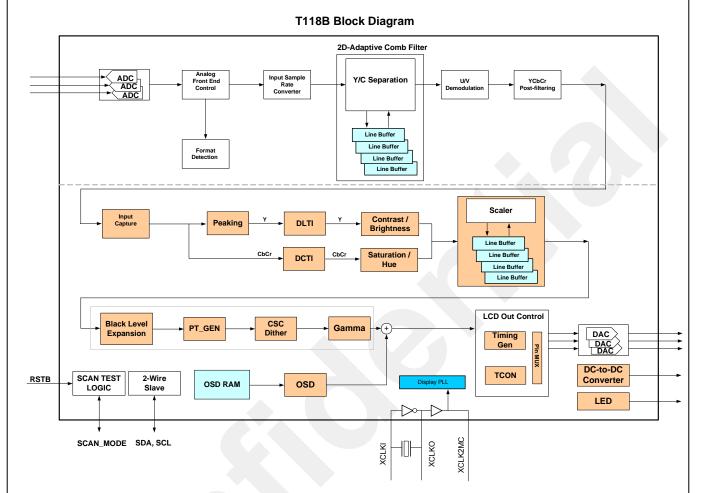

Figure 1-1 System Architecture

© Copyright 2006 Terawins, Inc.

### 1.5 System Configurations

### 1.6 Pinout Diagram

### 1.7 Pin Description

| Symbol        | Pin #          | Туре    | Description                                                        |

|---------------|----------------|---------|--------------------------------------------------------------------|

| Power Suppl   | lies           |         |                                                                    |

| VDD18         | 8,26           | PWR     | +1.8V digital core power supply                                    |

| VDD33         | 22,36          | PWR     | +3.3V digital output power supply,                                 |

| VD5A          | 38             | PWR     | +5.0V analog power supply                                          |

| VD33ADC1      | 63             | PWR     | +3.3V analog power supply for ADC                                  |

| VD33ADC2      |                |         |                                                                    |

| VD33DAC       | 47             | PWR     | +3.3V analog power supply for DAC                                  |

| VD33PWM       |                |         |                                                                    |

| GND           | 7,21,27,37     | GND     | Digital ground                                                     |

| VS18PLL       | 48             | GND     | Analog ground for PLL                                              |

| VS33ADC1      | 64             | GND     | Analog ground for ADC                                              |

| VS33ADC2      |                |         |                                                                    |

| VS33DAC       | 39             | GND     | Analog ground for DAC                                              |

| VS33PWM       | 62             | GND     | Analog ground for backlight inverter                               |

| Output Interf | ace Signals    |         |                                                                    |

| RSET          | 43             | AO      | DAC reference current adjustment                                   |

| VBFG          | 44             | AO      | Voltage reference output                                           |

| IOR           | 42             | AO      | Channel R current output                                           |

| IOG           | 41             | AO      | Channel G current output                                           |

| IOB           | 40             | AO      | Channel B current output                                           |

| CPH1          | 25             | DO      | Output data clock                                                  |

| CPH2/sD0      | 28             | DO      | Output data clock/the bit 0 of serial interfaced panel             |

| CPH3/sD1      | 29             | DO      | Output data clock/the bit 1 of serial interfaced panel             |

| VSO/STH1      | 23             | DO      | Vertical synchronization output signal.                            |

| HSO/POL       | 20             | DO      | Horizontal synchronization output signal.                          |

| DEN/STH2      | 24             | DO      | Horizontal data enable                                             |

| Timing Cont   | roller Interfa | ce Sig  | nals                                                               |

|               | 19             | DO      | Vertical Up/Down control                                           |

| RL            | 18             | DO      | Horizontal Right/Left control                                      |

| Q1H/sD2       | 30             | DO      | Source Driver Q1H/the bit 2 of serial interfaced panel             |

| LP/sD3        | 31             | DO      | Latch pulse for source driver/the bit 3 of serial interfaced panel |

| GCLK/sD4      | 32             | DO      | Gate driver clock/the bit 4 of serial interfaced panel             |

| GOE/sD5       | 33             | DO      | Gate driver output enable/the bit 5 of serial interfaced panel     |

| STV1/sD6      | 34             | DO      | Gate Driver start pulse/the bit 6 of serial interfaced panel       |

| STV2/sD7      | 35             | DO      | Gate Driver start pulse/the bit 7 of serial interfaced panel       |

| VCOMAMP       | 45             | DO      | Analog VCOM amplitude                                              |

| VCOMDC        | 46             | DO      | Analog VCOM DC offset                                              |

| 2-wire serial |                |         |                                                                    |

| SCL           | 11             | DI      | 2-wire serial bus clock. Power down does not affect SCL.           |

| SDA/IICA3     | 10             | I/O     | 2-wire serial bus data. Power down does not affect SDA.            |

| Configuratio  | n interface S  | Signals |                                                                    |

| CPUINT        | 12             | 1/0     | Internal Interrupt.                                                |

| RSTB          | 9              | DI      | Whole chip reset. (Internal Pull-up)                               |

|               | J              | וט      |                                                                    |

#### **Table 1-1 Pin Description**

| Symbol        | Pin #        | Туре    | Description                                            |

|---------------|--------------|---------|--------------------------------------------------------|

| ADC Interfac  | е            |         |                                                        |

| AY1           | 1            | AI      | Analog input 1 of input channel 2                      |

| AY0           | 2            | AI      | Analog input 0 of input channel 2                      |

| ACR1          | 3            | AI      | Analog input 1 of input channel 1                      |

| ACR0          | 4            | AI      | Analog input 0 of input channel 1                      |

| ACB1          | 5            | AI      | Analog input 1 of input channel 3                      |

| ACB0          | 6            | AI      | Analog input 0 of input channel 3                      |

| PLL Reference | ce Clock     |         |                                                        |

| XTALI         | 13           | DI      | Output PLL reference clock input                       |

| XTALO         | 14           | DO      | Output PLL reference clock output                      |

| XCLK2MC       | 15           | DO      | Buffered XTALI for external microprocessor.            |

| Power Manag   | gement Inter | rface S | ignals                                                 |

| PWM1          | 16           | DO      | Pulse Width Modulation for volume/backlight control.   |

| PWM2          | 17           | DO      | Pulse Width Modulation for volume/backlight control.   |

| VEA           | 49           | AO      | Error amplifier output                                 |

| CSS           | 50           | AO      | Soft start pin                                         |

| VFB           | 51           | AI      | Feedback of Lamp current                               |

| CEXT          | 52           | AO      | Switching frequency of DC-DC converter                 |

| VPWM          | 53           | AO      | PWM output, connect to external N-channel power MOSFET |

| VEAL          | 54           | AO      | Error Amplifier output                                 |

| VFBL          | 55           | AI      | Feedback of Lamp current                               |

| VPWML         | 56           | AO      | PWM output, drive NMOSFET switch                       |

| CSSL          | 57           | AO      | Soft start pin                                         |

| CEXTL         | 58           | AO      | Switching frequency of Inverter                        |

| VlsenL        | 59           | AI      | Current sense                                          |

| Vlsen         | 60           | AI      | Current sense                                          |

| NC            | 61           | N/A     |                                                        |

### 2 Theory of Operations

### 2.1 I<sup>2</sup>C Command Protocol

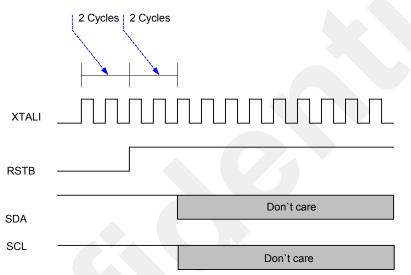

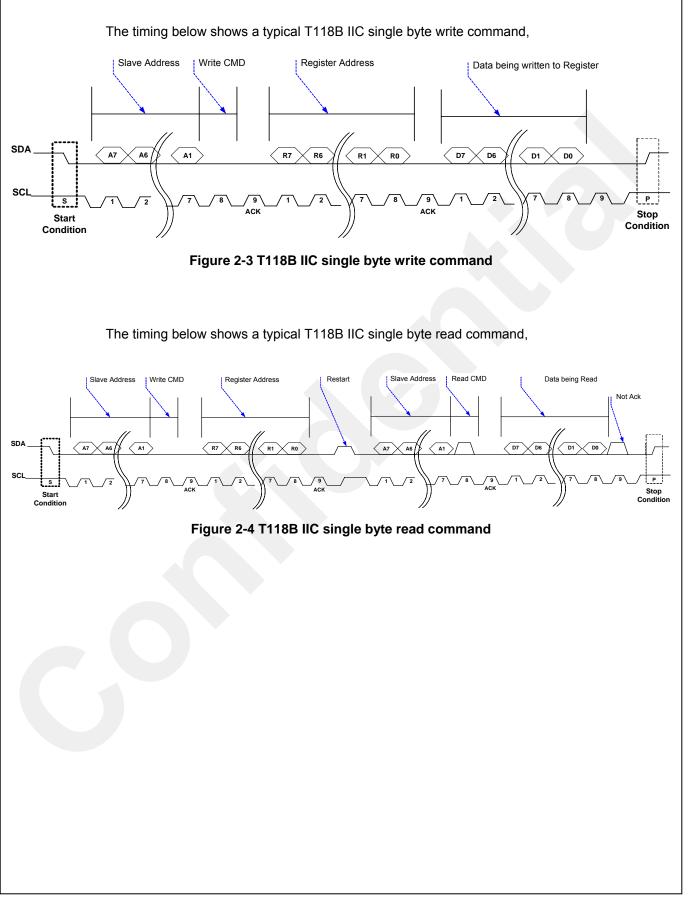

Before your tester writes I<sup>2</sup>C commands to T118B, slave address must be set at 50h. The timing sequence can be shown as below. After 4 cycles, the tester can get started IIC commands. SDA(A3) can affect slave address. Set low for 40h. Set high for 50h.

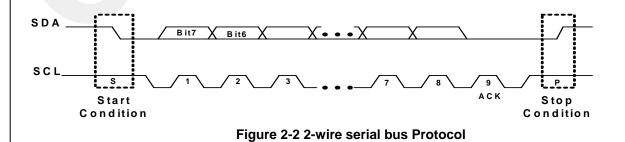

Figure 2-1 Power-up initialization

When tester issues commands to the T118B, the only way the user can program the T118B is using the 2-wire serial bus protocol. This section describes the 2-wire serial bus protocol. Data transfers on the 2-wire serial bus are initiated with a START condition and are terminated with a STOP condition. Normal data on the SDA line must be stable during the high period of the SCL. The transition on the SDA is only allowed while SCL is low. The START condition is unique case and is defined by a high-to-low transition on the SDA while the SCL is high. The STOP condition is a unique case and is defined by a low-to-high transition on the SDA while the SCL is high. Each data packet on the 2-wire serial bus consists of 8 bits of data followed by an ACK bit. Data is transferred with MSB first. The transmitter releases the SDA line during the ACK bit and the receiver of data transfer must drive the SDA line low during the ACK bit to acknowledge receipt of the data. The frequency of SCL can be from 50 Khz up to 1 Mhz.

### 2.2 Analog Front End

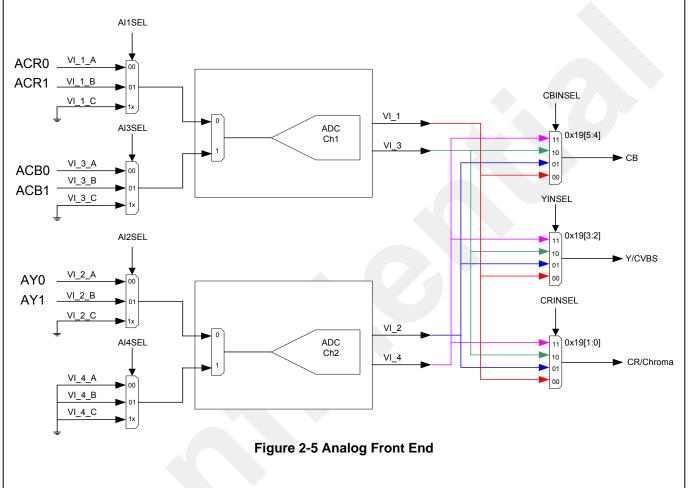

T118B contains 2 ADCs in Analog Front End. Each channel of ADCs can digitalize SDTV signals from analog to digital. The figure shown below can describe how to select a SDTV signal from 2 inputs prior to ADCs.

### 2.3 Y/C Separation and Chroma Decoder

A composite video has luma(Y) and chroma(C) information mixed in the same video signal. This video signal can also be represented by the equation below,

CVBS = Y + U \* Sin(wt) + V \* cos(wt)

Where  $w = 2\pi f_{sc}$ ,  $f_{sc}$  =3.58Mhz if NTSC,  $f_{sc}$  =4.43Mhz if PAL

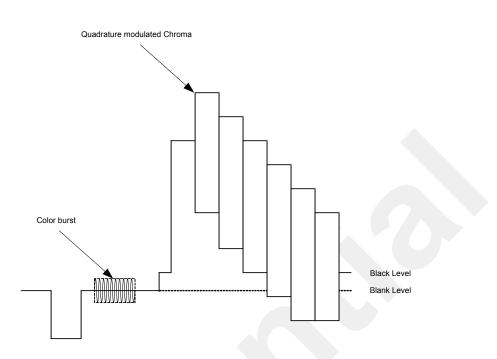

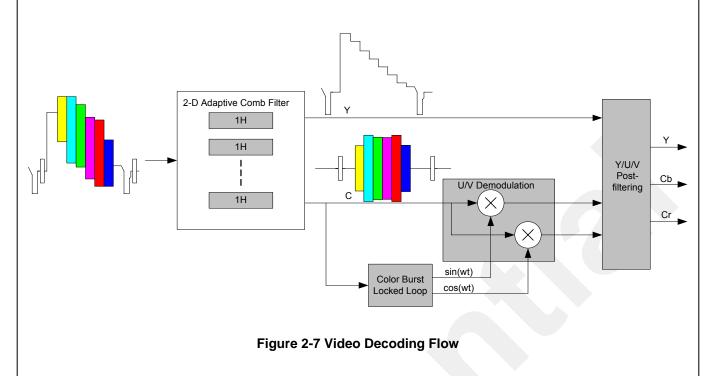

The figure below shows a typical composite signal. The 2-D adaptive comb filter inside T118B is designed to separate Y and C from a composite video signal.

#### Figure 2-6 Typical Color SDTV Signal

. The conventional 3-line comb filter fails to separate Y and C if there is a vertical transition. The 2-D adaptive comb filter is based on equally weighting factors that color changes along vertical and horizontal edges. Let the amount of color change along vertical and horizontal direction DCv and DCh, the weighting factor can be expressed as following equations,

$$Wh = \frac{DCv}{DCv + DCh}$$

$$Wv = \frac{DCh}{DCv + DCh}$$

By employing adaptive method, chroma can be recovered by following equation,  $C = Ch^*Wh + Cv^*Wv$

After Y/C separation, Y and C should look like waveforms shown as in following figure. Y only contains low frequency part, while C contains high frequency part which is centered around subcarrier  $f_{sc}$ .

### 2.4 Digital Color Transient Improvement (DCTI)

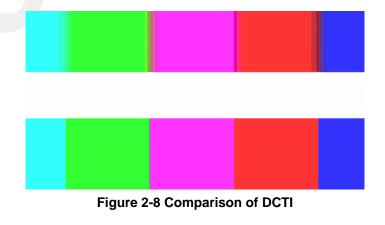

Usually, a composite or S-video SDTV signal may have bandwidth limitation that causes the loss chroma detail around two different color bars. Two pictures shown below illustrate the result before and after DCTI block. Without DCTI(the upper picture), we may see color transient wider than several pixels. A slow transient edge usually blurs image. T118B DCTI algorithm can sharpen those color transient edges. The lower picture shows that chroma data is enhanced by increasing the slope of edge transient without introducing the ring effects.

### 2.5 Digital Luminance Transient Improvement (DLTI)

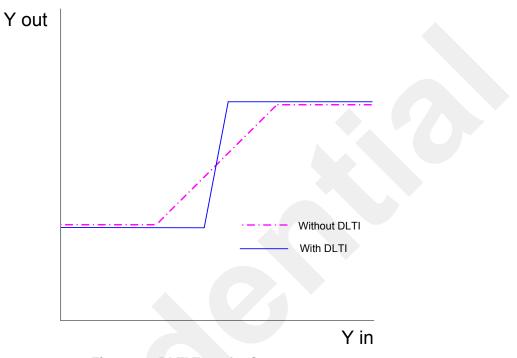

The Digital Luminance Transient Improvement is intended to sharpen luminance edge transient. The figure shown below is DLTI transfer function. DLTI doesn't increase peak-to-peak amplitude; rather it turns sloped waveforms into rectangular waveforms.

Figure 2-9 DLTI Transfer Curve

#### 2.6 FIR Scaler

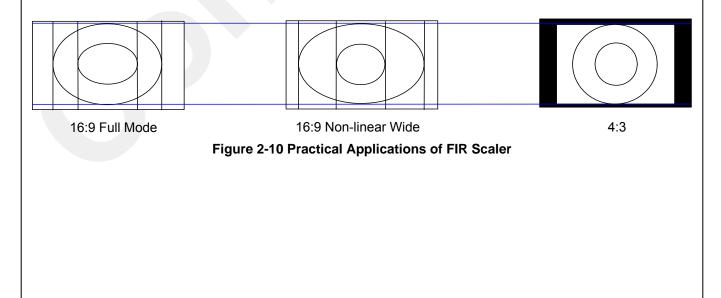

FIR Scaler can scale input H/V sizes to fit any LCD panel resolution. The flexible and independent H/V scalers allow users to program display area in 16:9 Full mode, 16:9 non-linear wide mode and 4:3 mode. FIR scaler also provides coefficient-based 2-D sharpness that can sharpen detail of picture.

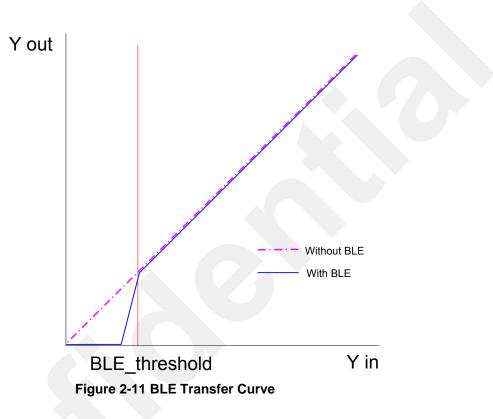

### 2.7 Black-Level Extension (BLE)

Black Level Expansion (BLE) can enhance image contrast that makes dark regions of image darker, while bright regions remain unchanged. The figure shown below is BLE transfer function.

$Yout = Yin - (Yoffset - Yin) * BLE \_ Gain / 16$ Where *Yoffset* and *BLE \_ Gain* can be programmed by register P0\_96h.

### 2.8 Color Space Converter

A pixel in YCbCr color space can be converted to RGB color space by using following equations,

$$\begin{split} R &= YCoefCSC*(Y-16) + CrCoef \ _R*(Cr-128) \\ G &= YCoefCSC*(Y-16) - CrCoef \ _G*(Cr-128) - CbCoef \ _G*(Cb-128) \\ B &= YCoefCSC*(Y-16) + CbCoef \ _B*(Cb-128) \end{split}$$

Where YCoefCSC is in 1.7-bit fixed point with default 1.164.  $CrCoef \_R$  in 1.7-bit fixed point with default 1.596.  $CrCoef \_G$  in 0.8-bit fixed point with default 0.813.  $CbCoef \_G$  in 0.8-bit fixed point with default 0.392.  $CbCoef \_B$  in 2.6-bit fixed point with default 2.017

The equations shown as below correspond to a typical YCbCR-to-RGB converter. In T118B, we make those coefficients adjustable.

$$R = 1.164 * (Y - 16) + 1.596 * (Cr - 128)$$

$$G = 1.164 * (Y - 16) - 0.813 * (Cr - 128) - 0.392 * (Cb - 128)$$

$$B = 1.164 * (Y - 16) + 2.017 * (Cb - 128)$$

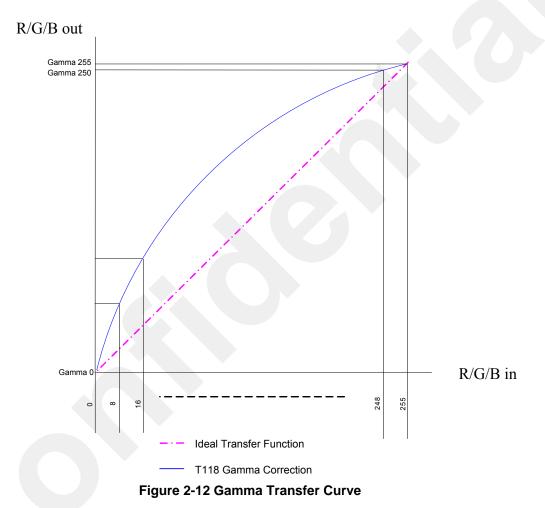

### 2.9 Gamma Correction

The relation between input video signal and LCD panel may exist non-linear transfer function such as figure shown below,

T118B uses 3 independent 256-entry RAM-based LUTs that are allowed to be programmed each point via register at P0\_93h and P0\_94h.

## 2.10 OSD

### 2.10.1 OSD Access

| I/O Port        | Index | Default | Description                                                                                               |

|-----------------|-------|---------|-----------------------------------------------------------------------------------------------------------|

|                 | 00h   | 00h     | OSD Control Register                                                                                      |

|                 | 01h   | 00h     | Character Delay_1                                                                                         |

|                 | 02h   | 10h     | Character Delay_2                                                                                         |

|                 | 03h   | 08h     | Character Delay_3                                                                                         |

|                 | 04h   | 00h     | Alpha Blending Control                                                                                    |

|                 | 05h   | 38h     | Char_RAM Base Address                                                                                     |

|                 | 06h   | 40h     | Char_RAM Stop Address                                                                                     |

| A0h – OSD_Index | 07h   | 00h     | Reserved                                                                                                  |

| A1h – OSD_Data  | 08h   | 00h     | Reserved                                                                                                  |

|                 | 09h   | 0Ah     | Blinking Control                                                                                          |

|                 | 0Ah   | 00h     | Bit_Map Window Size : Height Upper Bits and BMP Enlarge Control                                           |

|                 | 0Bh   | 0Ah     | Bit_Map Window Size : Width                                                                               |

|                 | 0Ch   | 66h     | Bit_Map Window Size : Height                                                                              |

|                 | 0Dh   | 00h     | Reserved                                                                                                  |

|                 | 0Eh   | -       | OSD LUT RAM data port (Write Only)                                                                        |

|                 | 0Fh   | 00h     | Char Control Register                                                                                     |

| A2h – ORAM_AL   |       | 00h     | OSD RAM Low Address Port of Starting Access                                                               |

| A3h – ORAM_AH   |       | 00h     | OSD RAM High Address Port of Starting Access                                                              |

| A4h – ORAM_D    |       | 00h     | OSD RAM Data Port (Low Byte first, then High Byte). After two Writes, the address will be increased by 1. |

#### Table 2-1 OSD Access

### 2.10.2 RAM Addressing A[9:0]

### 2.10.3 Character RAM format

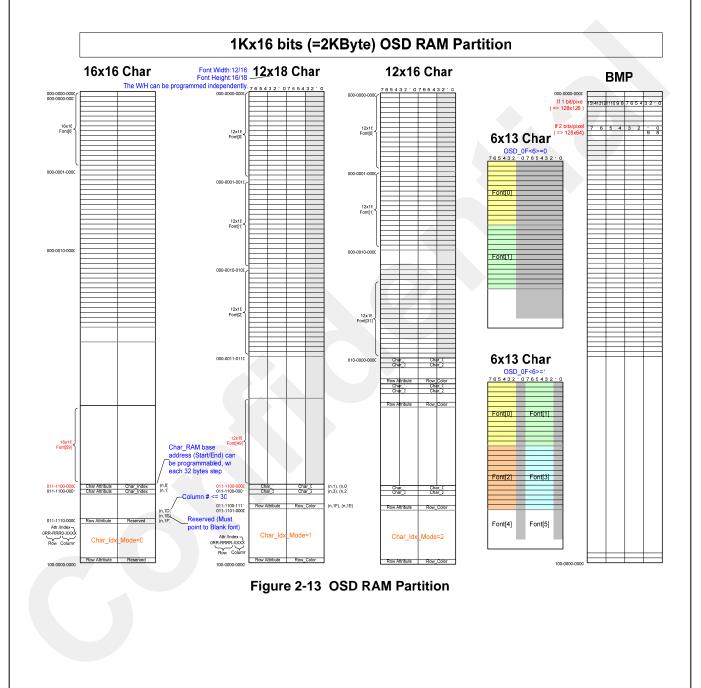

In Character Mode (contrast to Bit\_Map Mode), the Characters displayed on OSD can be grouped to few rows; each row has its own row attribute which defines the behavior of current character row. And, there is maximum 30 characters in one row, each character has 1~2 bytes to define its character font number and its colors. Due to providing more flexible menu programming, T102 supports three character modes:

#### Table 2-2 Character Index Modes (Char\_Idx\_Mode)

#### Char\_Idx\_Mode = 0

|                  | 6[2:0] |      | Blink |          | FG    | 6[3:0] |     |     |        | Inde  | x (Char | 2       |       | XXX-XXX0-0000 |   |

|------------------|--------|------|-------|----------|-------|--------|-----|-----|--------|-------|---------|---------|-------|---------------|---|

|                  | G[2:0] |      | Blink |          |       | [3:0]  |     |     |        |       | x (Char | - /     |       | XXX-XXX0-0001 |   |

|                  | 5[2:0] |      | Blink |          |       | 5[3:0] |     |     |        |       | x (Char |         |       | XXX-XXX0-0010 |   |

|                  |        |      |       |          |       |        |     |     |        |       |         |         |       | -             |   |

|                  |        |      |       |          |       |        |     |     |        |       |         |         |       |               |   |

| BG               | 6[2:0] |      | Blink |          | FG    | 6[3:0] |     |     |        | Index | (Char   | 29)     |       | XXX-XXX1-1101 |   |

| 0                | 00b    |      | 0     |          | 00    | 00b    |     |     | In     | dex t | o Blank | Char    |       | XXX-XXX1-1110 |   |

| v_BG             |        | Ro   | w_Ga  | ар       |       | CHS    | CWS |     |        |       |         |         |       | XXX-XXX1-1111 |   |

|                  |        |      |       |          |       |        |     |     |        |       |         |         |       |               |   |

|                  |        |      |       |          |       |        |     |     |        |       |         |         |       |               |   |

| r_ldx            | _Mo    | de = | 1     |          |       |        |     |     |        |       |         |         |       |               |   |

| 15               | 14     | 13   | 12    |          | 10    | 9      | 8   | 7   | 6      | 5     | 4 3     |         | 1 0   |               |   |

| 3G               | FG     |      |       | Index (C |       |        |     | BG  | FG     |       |         | (Char_  |       | XXX-XXX-0000  |   |

| BG               | FG     |      |       | Index (C | Char_ | _3)    |     | BG  | FG     |       | Index   | (Char_  | 2)    | XXX-XXX-0001  |   |

|                  |        |      |       |          |       |        |     |     |        |       |         |         |       | l             |   |

|                  |        |      |       |          |       |        |     |     |        |       |         |         |       | ſ             | , |

| 3G               | FG     |      |       | Index (C | Char_ | 27)    |     | BG  | FG     |       | Index   | Char_2  | :6)   | XXX-XXXX-1101 |   |

| 3G               | FG     |      |       | Index (C | Char_ | 29)    |     | BG  | FG     |       | Index   | Char_2  | :8)   | XXX-XXXX-1110 |   |

| v_BG             |        | Ro   | w_Ga  | ар       |       | CHS    | CWS | BG  | _C[2:0 | )]    |         | FG_C    | [3:0] | XXX-XXXX-1111 |   |

|                  |        |      |       |          |       |        |     |     |        |       |         |         |       |               |   |

|                  |        |      |       |          |       |        |     |     |        |       |         |         |       |               |   |

| _                | (_Mo   |      |       |          |       |        |     | I _ |        | _     |         |         |       |               |   |

| 15               | 14     | 13   | 12    |          | 10    | 9      | 8   | 7   | 6      | 5     |         | 2       |       |               |   |

| BG               | FG[1   |      |       |          |       | nar_1) |     | BG  | FG[1   |       |         | ex (Cha |       | XXX-XXX-0000  |   |

| BG               | FG[1   | 1:0] |       | Index    | x (Cr | nar_3) |     | BG  | FG[1   | []]   | Ind     | ex (Cha | r_2)  | XXX-XXX-0001  |   |

|                  |        |      |       |          |       |        |     |     |        |       |         |         |       | ļ             | - |

|                  |        |      |       |          |       |        |     |     |        |       |         |         |       | _ (           | , |

|                  | FG[1   | l:0] |       | Index    | (Ch   | ar_27) |     | BG  | FG[1   | [:0]  | Inde    | x (Char | _26)  | XXX-XXXX-1101 |   |

| 3G               |        |      |       | Index    | (Ch   | ar_29) |     | BG  | FG[1   | [:0]  | Inde    | x (Char | _28)  | XXX-XXXX-1110 |   |

| 3G<br>3G<br>v_BG | FG[1   |      | w_Ga  |          |       | CHS    | CWS |     | _C[2:0 |       |         | => LUT  |       |               |   |

#### 2.10.3.1 Character Index Data (Address to Font Select)

| Address Offset:<br>Default Value: |    | no (part of menu char)<br>XXh | Access:<br>Size:                                                                                                                                                                                                                                                      | Write Only<br>8 bits |  |  |

|-----------------------------------|----|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|

| Bit Access Symbol                 |    |                               | Description                                                                                                                                                                                                                                                           |                      |  |  |

| [7:6]                             | WO | 00 or BG/FG                   | Depends on Char_Idx_Mode                                                                                                                                                                                                                                              |                      |  |  |

| [4:0]                             | WO |                               | Character Address (Index), selects the character font (i.e., 0,1,2,<br>A,B,C, a,b,c,\$,%,). If the value is number N, then it selects the N <sup>th</sup><br>font, and that font starting address is (N x Font_Height ). The<br>Font Height is defined in OSD 0Fh<5>. |                      |  |  |

In Char\_Idx\_Mode=0, this Index is 8 bits, and selecting one of total 256 fonts (but OSD RAM is small, for 64 fonts maximum)

In Char\_Idx\_Mode=1, this Index is 6 bits, and selecting one of total 64 fonts

In Char\_Idx\_Mode=2, this Index is 5 bits, and selecting one of total 32 fonts

#### 2.10.3.2 Character Attribute

| Address Offset: | no (part of menu char) | Access: | Write Only |  |

|-----------------|------------------------|---------|------------|--|

| Default Value:  | XXh                    | Size:   | 8 bits     |  |

| Bit   | Access | Symbol           | Description                                                                                                         |

|-------|--------|------------------|---------------------------------------------------------------------------------------------------------------------|

| [7:5] | WO     | BG_R, BG_G, BG_B | Background R/G/B Color (Intensity=0). If all 0, then no background, i.e. transparent.                               |

| [4]   | WO     |                  | Enable this Character display with blinking feature. Refer to section 2.10.4.8 for detail blinking control.         |

| [3:0] | WO     |                  | Foreground R/G/B/Intensity Color. If the value is set as 0000b, then there will be no foreground, i.e. transparent. |

#### 2.10.3.3 Row Attribute

Address Offset:no (part of menu char)Access:Write OnlyDefault Value:XXhSize:8 bits

| Bit   | Access | Symbol    | Description                                                                                                                                                                    |

|-------|--------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]   | WO     | RGAP_BG   | Color Select of Row Gap. Set 1 for selecting the same color of background of current row character, 0 for selecting transparent color.                                         |

| [6:2] | WO     | RGAP[4:0] | Row Gap (=Row Space). Inserted range is $4 \times (31_d \sim 0)$ scan lines before current Row.                                                                                |

| [1]   | WO     | CHS       | Character Height Select. Set 1 for double height, 0 for single height.                                                                                                         |

| [0]   | WO     | CWS       | Character Width Select. Set 1 for double width, 0 for single width.<br>When set to 1, only the even numbered characters will be shown, odd<br>numbered characters are skipped. |

### 2.10.4 OSD Configuration Register

#### 2.10.4.1 Cfg\_00h – OSD Control Register

| Address Offset:<br>Default Value: |        | OSD_00h<br>00h | Access: Read/Write<br>Size: 8 bits                                                |  |  |

|-----------------------------------|--------|----------------|-----------------------------------------------------------------------------------|--|--|

| Bit                               | Access | Symbol         | Description                                                                       |  |  |

| [7]                               | R/W    | OSD_En         | Enabling the OSD function. Set 1 for enabling, 0 for disabling OSD                |  |  |

| [6]                               | R/W    | Bit_Map        | Select Bit Mapped OSD display mode. Set 1 for Bit_Map Mode, 0 for Character Mode. |  |  |

| [5]                               | R/W    | Bit2PP         | Two bits per Pixel for Bit_Map mode. Set 1 for 2 Bits/Pixel, 0 for 1 Bit/Pixel.   |  |  |

| [4]                               | RO     | Reserved       |                                                                                   |  |  |

| [3]                               | R/W    | Font_Hx2       | Character mode, fonts height double.                                              |  |  |

| [2]                               | R/W    | Early_hDE      | let OSD a little shift left.                                                      |  |  |

| [0]                               | R/W    | Font_WxN       | Character mode, fonts width enlarge. Value 0~3 = x1, x2, x3, x4                   |  |  |

#### 2.10.4.2 Cfg\_01h – Character Delay\_1

Address Offset: OSD\_01h Default Value: 00h

01h

Access: Read/Write Size: 8 bits

| Bit   | Access | Symbol      | Description                                                                                                                                                                      |

|-------|--------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]   | RO     | Reserved    |                                                                                                                                                                                  |

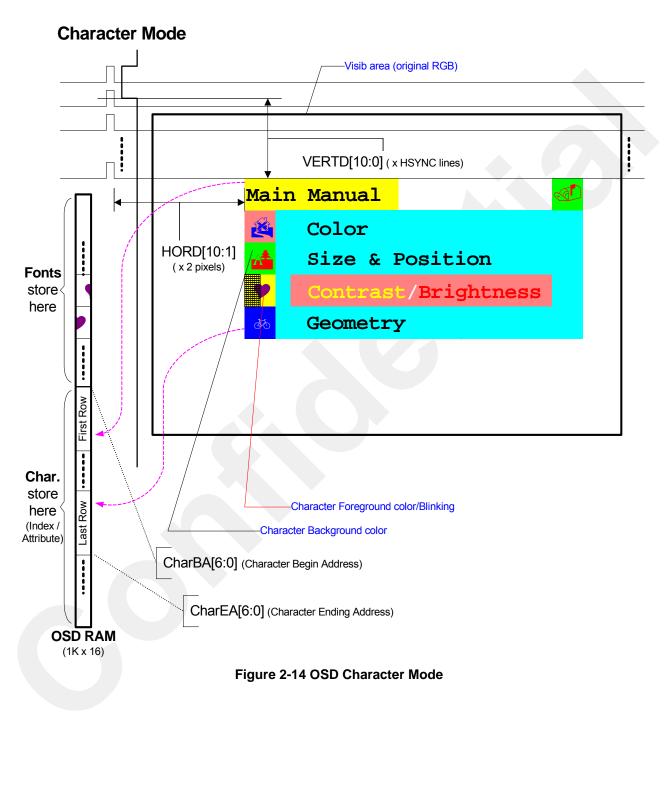

| [6:4] | R/W    | VERTD[10:8] | Vertical Starting Position (Upper bits) of Character displaying. These bits with Cfg_03h, total 11 bits, become 2048 steps, with an increment one pixel per step for each field. |

| [3]   | RO     | Reserved    |                                                                                                                                                                                  |

| [2:0] | R/W    | HORD[10:8]  | Horizontal Starting Position (Upper bits) of Character displaying.<br>These bits with Cfg_02h, total 11 bits, become 2048 steps, with an<br>increment one pixel per step.        |

#### 2.10.4.3 Cfg\_02h – Character Delay\_2

|       | ss Offset:<br>It Value: | OSD_02h<br>10h | Access: Read/Write<br>Size: 8 bits                                                                                                                                             |      |

|-------|-------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Bit   | Access                  | Symbol         | Description                                                                                                                                                                    |      |

| [7:0] | R/W                     | HORD[7:0]      | Horizontal Starting Position (Lower bits) of Character displaying.<br>These bits with Cfg_01h<2:0>, total 11 bits, become 2048 steps, with<br>an increment one pixel per step. | with |

#### 2.10.4.4 Cfg\_03h - Character Delay\_3

|       | ss Offset:<br>It Value: | OSD_03h<br>08h | Access:<br>Size:                                                                                                                                                                       | Read/Write<br>8 bits |

|-------|-------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Bit   | Access                  | Symbol         | Description                                                                                                                                                                            |                      |

| [7:0] | R/W                     |                | Vertical Starting Position (Lower bits) of Character displaying. This register with Cfg_01h<6:4>, total 11 bits become 2048 steps, with an increment one line per step for each field. |                      |

### 2.10.4.5 Cfg\_04h – Alpha Blending Control

|       | ss Offset:<br>t Value: | OSD_04h<br>00h | Access:<br>Size:                                              | Read/Write<br>8 bits                                                                                                                                                                                                              |

|-------|------------------------|----------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit   | Access                 | Symbol         |                                                               | Description                                                                                                                                                                                                                       |

| [7]   | R/W                    | FG_NoAB        | set to one. Do<br>Character for                               | ter ForeGround portion will be exclusive to be blended if<br>efault is 0 as no matter the current displayed pixels are in<br>eground or border/shadow or background or in OSD<br>ill be alpha blended with original Video source. |

| [6:3] | RO                     | Reserved       |                                                               |                                                                                                                                                                                                                                   |

| [2:0] | R/W                    | AB_Set[2:0]    | If set 000b, a<br>8/8 * OSD dis<br>If set 001b, b<br>display; | ng percentage (n/8).<br>Ipha blending is disabled (0/8 * Original Video Source +<br>splay);<br>Iending as 1/8 * Original Video Source + 7/8 * OSD<br>ding as N/8 * Original Video Source + (8-N)/8 * OSD                          |

### 2.10.4.6 Cfg\_05h – Char\_RAM Base Address

| Address Offset:<br>Default Value: |        | OSD_05h<br>38h | Access:<br>Size:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Read/Write<br>8 bits |

|-----------------------------------|--------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Bit                               | Access | Symbol         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |

| [7]                               | RO     | Reserved       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |

| [6:0]                             | R/W    | CharBA[6:0]    | Programmable Character RAM Base Address. Those 7 bits become<br>128 steps, each step is 32 Bytes (one Character Row include<br>Char_Index, Char_Attr, Row_Attr; i.e. 30 column maximum for each<br>Row). The actual address will be 0RR-RRRX-XXXX (in<br>Char_Idx_Mode=0 and the CharBA[0] should be 0), or 0RR-RRRR-<br>XXXX (for Char_Idx_mode=1 or 2). The RR-RRRR means the value<br>of CharBA[6:0]; the X-XXXX is the nth Char Column. For trading off<br>Font number and Character number in a single RAM (this version is<br>1Kx16 bits), user should carefully setting this register. |                      |

### 2.10.4.7 Cfg\_06h - Char\_RAM Stop Address

| Address Offset: | OSD_06h | Access: | Read/Write |

|-----------------|---------|---------|------------|

| Default Value:  | 40h     | Size:   | 8 bits     |

| Bit   | Access | Symbol   | Description                                                                                                                                                                                                                                                                                                                                           |

|-------|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]   | RO     | Reserved |                                                                                                                                                                                                                                                                                                                                                       |

| [6:0] | R/W    |          | Programmable Character RAM Stop/End Address (Available if<br>Revision ID >= 0h). Those 7 bits become 128 steps, each step is 32<br>bytes. The actual stop address will be 0RR-RRX-XXXX (The RRRR-<br>RRR means the value of CharEA[6:0]; the X-XXXX is the nth Char<br>Column. and OSD will be displayed for Character Row >= CharBA<br>and < CharEA. |

#### 2.10.4.8 Cfg\_09h – Blinking Control

| Address Offset:<br>Default Value: |        | OSD_09h<br>0Ah  | Access:<br>Size:                                                                                                                                                                                                    | Read/Write<br>8 bits                              |  |

|-----------------------------------|--------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--|

| Bit                               | Access | Symbol          |                                                                                                                                                                                                                     | Description                                       |  |

| [7]                               | R/W    | En_Global_Blink | Enable whole                                                                                                                                                                                                        | Enable whole OSD Characters blinking if set to 1. |  |

| [6:4]                             | RO     | Reserved        |                                                                                                                                                                                                                     |                                                   |  |

| [3:2]                             | R/W    | BCLK[1:0]       | Blinking Frequency Select (internal 4x BCLK for Blinking State Machine). Set 00b for Refresh Rate /16; 01b for 1/32; 10b for 1/64; 11b for 1/128.                                                                   |                                                   |  |

| [1:0]                             | R/W    | Duty[1:0]       | For adjusting the blinking duty cycle, Set:<br>00b for Global Blink Off, i.e., 0% Background, 100% OSD.<br>01b for 25% Background, 75% OSD.<br>10b for 50% Background, 50% OSD.<br>11b for 75% Background, 25% OSD. |                                                   |  |

#### 2.10.4.9 Cfg\_0Ah – Bit\_Map Window Size: Height Upper Bits

| Address Offset:<br>Default Value: |        | OSD_0Ah<br>00h      | Access:<br>Size:                                                                                                                                                                     | Read/Write<br>8 bits |  |

|-----------------------------------|--------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|

| Bit                               | Access | Symbol              |                                                                                                                                                                                      | Description          |  |

| [7:6]                             | RO     | Reserved            |                                                                                                                                                                                      |                      |  |

| [5:4]                             | R/W    | BMH[9:8]            | Bit Map Window Height Upper bits (only available in Bit_Map mode).<br>Please refer to OSD_0Ch for detail. User must be careful of the OSD<br>RAM size limitation.                    |                      |  |

| [3:2]                             | R/W    | BMP_Height_xN [1:0] | Bit Map Window Vertical Enlarge (only available in Bit_Map mode).<br>Set 00b for 1 line per dot, 01b for 2 lines per dot, 10b for 3 lines per<br>dot, 11b for 4 lines per dot.       |                      |  |

| [1:0]                             | R/W    | BMP_Width_xN[1:0]   | Bit Map Window Horizontal Enlarge (only available in Bit_Map mode).<br>Set 00b for 1 pixel per dot, 01b for 2 pixels per dot, 10b for 3 pixels<br>per dot, 11b for 4 pixels per dot. |                      |  |

#### 2.10.4.10 Cfg\_0Bh - Bit\_Map Window Size: Width

| Address Offset:<br>Default Value: |     | OSD_<br>0Ah | _0Bh        | Acce<br>Size                             |                                                                                                                                                                                                                                                                                                                                                                        | Read/Write<br>8 bits |    |

|-----------------------------------|-----|-------------|-------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----|

| Bit Access Symbol                 |     |             | Description |                                          |                                                                                                                                                                                                                                                                                                                                                                        |                      |    |

| [7:0]                             | R/W |             | BMW[7:0]    | This re<br>step is<br>Bit2PP<br>2 bits/p | Bit Map Window Width Lower bits (only available in Bit_Map mod<br>This register has 8 bits, i.e., 256 steps (value 00h is not valid), estep is 16 or 8 dots depends on Bit2PP (OSD_00h<5>) setting.<br>Bit2PP=0 (i.e., 1 bit/pixel), each step is 16 dots. When Bit2PP=1<br>2 bits/pixel), each step is 8 dots. User must be careful of the OS<br>RAM size limitation. |                      | en |

### 2.10.4.11 Cfg\_0Ch – Bit\_Map Window Size: Height

| Address Offset: | — | Access: | Read/Write |

|-----------------|---|---------|------------|

| Default Value:  |   | Size:   | 8 bits     |

|                 |   |         |            |

| Bit   | Access | Symbol | Description                                                                                                                                                                                                                                                                          |

|-------|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | R/W    |        | Bit Map Window Height Lower bits (only available in Bit_Map mode).<br>This register combined with OSD_0Ah<5:4> and become 10 bits, i.e.<br>1024 height step: all 0 for reserved, 10'h001 for 1 line, 10'h3FF for<br>1023 lines. User must be careful of the OSD RAM size limitation. |

| 2.10.4 | 2.10.4.12 Cfg_0Dh – Bit_Map Window Size: Height                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |                     |                             |                                                                                                                                                                                                                                          |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ss Offset:<br>t Value: | OSD_0Dh<br>86h      | Access:<br>Size:            | Read/Write<br>8 bits                                                                                                                                                                                                                     |  |

|        | Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Access                 | Symbol              |                             | Description                                                                                                                                                                                                                              |  |

|        | [7:3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W                    | FontH[4:0]          | Font Height. \              | Value >=1                                                                                                                                                                                                                                |  |

|        | [2:0] R/W FontW[3:1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                        | FontW[3:1]          | Font WeigthX                | K2. Value 3~7 = width 6, 8,, 14; others = width 16                                                                                                                                                                                       |  |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |                     |                             |                                                                                                                                                                                                                                          |  |

| 2.10.4 | .13 Cf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | a 0Eh – O              | SD Color LUT RAM Da | ata Port                    |                                                                                                                                                                                                                                          |  |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ss Offset:             | OSD 0Eh             | Access:                     | Write Only                                                                                                                                                                                                                               |  |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | t Value:               | XXh                 | Size:                       | 8 bits                                                                                                                                                                                                                                   |  |

|        | Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Access                 | Symbol              |                             | Description                                                                                                                                                                                                                              |  |

|        | [7:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W                    | LUT_D[7:0]          |                             | be written to (or read from) OSD Color LUT RAM. After<br>r Write access to LUT RAM, then the LUT address will be                                                                                                                         |  |

|        | <pre>whenever the index value is programmed to non-0Eh value, the OSD Color LUT RAM can not be access,<br/>and the pointer always kept at 1.<br/>Note: The order to fill LUT RAM is:<br/>1. LUT[1]_Green/Blue<br/>2. LUT[1]_0000b/Red<br/>3. LUT[2]_Green/Blue<br/>4. LUT[2]_0000b/Red<br/>5. LUT[3]_Green/Blue<br/>6<br/>29. LUT[15]_Green/Blue<br/>30. LUT[15]_0000b/Red<br/>31. LUT[0]_Green/Blue<br/>32. LUT[0]_0000b/Red<br/>33. LUT[1]_Green/Blue<br/>34. LUT[1]_O000b/Red<br/></pre> |                        |                     |                             |                                                                                                                                                                                                                                          |  |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _                      |                     |                             |                                                                                                                                                                                                                                          |  |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ss Offset:<br>t Value: | OSD_0Fh<br>00h      | Access:<br>Size:            | Read/Write<br>8 bits                                                                                                                                                                                                                     |  |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |                     | 0120.                       |                                                                                                                                                                                                                                          |  |

|        | Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Access                 | Symbol              |                             | Description                                                                                                                                                                                                                              |  |

|        | [7]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RO                     | Reserved            |                             |                                                                                                                                                                                                                                          |  |

|        | [6]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W                    | FontW_Byte          | RAM utilizatio >=10. When s | dth = 6 or 8 (and only), this bit is optional for the font<br>on. When clear to 0, fonts stored in RAM as font width<br>set to 1, fonts stored in RAM: Even-indexed fonts put at<br>in RAM, and Odd-indexed fonts put at the low byte in |  |

|       |     |          | the high byte in RAM, and Odd-indexed fonts put at the low byte in RAM.                                                                                      |

|-------|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [5:4] | RO  | Reserved |                                                                                                                                                              |

| [3:2] | R/W |          | Character attribute/Index coding modes, 0 for original 2 bytes (256 index) mode. 1 for 1-byte (64 index) mode, 2 for 1-byte (32 index) mode, 3 for reserved. |

| [1:0] | R/W |          | OSD RAM access pointer behavior:<br>0X: Word (2-bytes) R/W; (Fonts, BMP, Character Menu)<br>10: Low byte only; 11: High byte only; (Character Menu)          |

### 2.10.5 Functional Description

#### 2.10.5.1 Host Access OSD RAM

#### 2.10.5.1.1 Writing Data

The OSD RAM size is 1Kx16, i.e., 1K word with each word is 2 bytes. The host interface is 8-bit data width, so whenever the host writes 2 times (one for data low byte, the other for data high byte) then it becomes one write with 16-bit data to OSD RAM. The ORAM\_D (OSD module base address + 04h) port when writing in the  $1^{st}/3^{rd}/5^{th}/7^{th}$ ..times, it will latch lower byte of OSD RAM writing data when the host want to program Font or Character, Attribute, BMP values; and when writing  $2^{nd}/4^{th}/6^{th}/8^{th}$ ... times, it will use this 8bits data as high byte and write both two bytes to OSD RAM.

#### 2.10.5.1.2 Reading Data

Read back data in OSD RAM is disabled.

#### 2.10.5.1.3 Access Address

The OSD RAM access pointer is programmed by the host write access to ORAM\_AL and ORAM\_AH ports. The OSD RAM size is 1Kx16, so the pointer is required to cover 1K words, i.e., 11 address lines => A[10:0]. When the host read these ORAM\_AL/ORAM\_AH ports, the pointer value reflects the current OSD RAM accessing pointer.

### 2.10.5.2 OSD Displaying in Character Mode

#### 2.10.5.3 OSD LUT Color Mapping

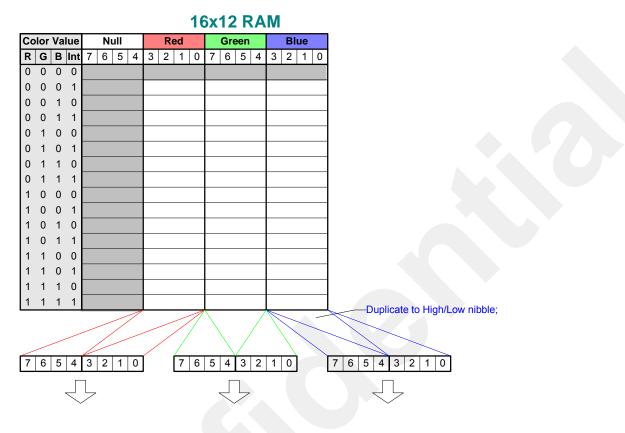

#### 1. Character Mode

Char\_Idx\_Mode=0, FG[3:0] as Color\_0= transparent; Color\_1~15= LUT[1..15] BG[2:0] as Color\_0= transparent; Color\_1~7= LUT[2,4,..14]

Char\_Idx\_Mode=1, FG as Color\_0= transparent; Color\_1= depends on its Row\_Attribute FG\_C[3:0], then redirect to transparent or LUT[1..15] BG as Color\_0= transparent; Color\_1= depends on its Row\_Attribute BG\_C[2:0], then redirect to transparent or LUT[2,4,..14]

Char\_Idx\_Mode=2, FG[1:0] as Color\_0= transparent; Color\_1~3= LUT[1..3] BG as Color\_0= transparent; Color\_1= depends on its Row\_Attribute BG\_C[2:0], then redirect to transparent; Color\_1= depends on its Row\_Attribute BG\_C[2:0], then redirect to transparent; Color\_1= depends on its Row\_Attribute BG\_C[2:0], then redirect to transparent or LUT[2,4,..14]

#### 2. Bit\_Map Mode

1 Bit/Pixel mode: Color\_0= transparent; Color\_1= LUT[1] 2 Bits/Pixel mode: Color\_0= transparent; Color\_1~3= LUT[1..3]

Figure 2-15 OSD Color Look Up Table

#### 2.10.5.4 Programming Examples

#### 2.10.5.4.1 Configuring OSD Function

To access OSD configuration registers, write register index to port A0h, and read/write data from port A1h. For example, set :

| IOW | A0h, 05h  | ; point to OSD_05h (Char Base Address register). |

|-----|-----------|--------------------------------------------------|

| IOR | A1h;      | ; get Char Base Address.                         |

| IOW | A0h, 06h  | ; point to OSD_06h (Char Stop Address register). |

| IOW | A1h, 3Eh; | ; Set Char Stop Address of current menu.         |

#### 2.10.5.4.2 Fill LUT RAM

LUT RAM size is 16 (address) x 12 (width). For example, need to fill LUT RAM as: LUT\_RAM[1]=F5Ah, ...LUT\_RAM[15]=EF0h

| IOW | A0h, 0Eh     | ; point to OSD_0Eh (LUT RAM Data port), this will let LUT RAM be<br>; access-able and pointer starts from 0h of LUT RAM. |

|-----|--------------|--------------------------------------------------------------------------------------------------------------------------|

| IOW | A1h, 5Ah;    | ; fill Green = 0101b and Blue = 1010h in LUT_RAM[1].                                                                     |

| IOW | A1h, 0Fh;    | ; fill Red = 1111b in LUT_RAM[1].                                                                                        |

|     |              | ; after this write, h/w will increase LUT RAM address to 2 automatically                                                 |

| IOW | A1h, F0h;    | ; fill Green = 1111b and Blue = 0000h in LUT RAM[15].                                                                    |

| IOW | A1h, 0Eh;    | ; fill Red = 1110b in LUT_RAM[15].                                                                                       |

|     |              | ; after this write, h/w will increase LUT RAM address to 0 automatically                                                 |

| IOW | A0h, non-0Eh | ; Disable LUT RAM programming.                                                                                           |

#### 2.10.5.4.3 Load Fonts to OSD RAM

OSD RAM size is 1K (address: 000h ~ 3FFh) x 16 (width). Fonts storing starts from address 000h. For example, loading some fonts to OSD RAM as: Font[0

| 0] is a | a space (a | all zero), Font[1] is a | character 2 with box, Font[14] is a graphic,                                            |

|---------|------------|-------------------------|-----------------------------------------------------------------------------------------|

|         | IOW        | A2h, 00h                | ; set OSD RAM starting access address low byte. (bit [7:0] as A[7:0])                   |

|         | IOW        | A3h, 00h;               | ; set OSD RAM starting access address high byte. (bit [3:0] as A[11:8])                 |

|         |            |                         | ; then the OSD RAM address pointer is set to 000h.                                      |

|         | IOW        | A4h, 00h;               | ; low byte of first row of Font[0].                                                     |

|         | IOW        | A4h, 00h;               | ; high byte of first row of Font[0], after this write, h/w will increase OSD            |

|         |            |                         | ;RAM address to 1 automatically                                                         |

|         | IOW        | A4h, 00h;               | ; low byte of 2 <sup>nd</sup> row of Font[0].                                           |

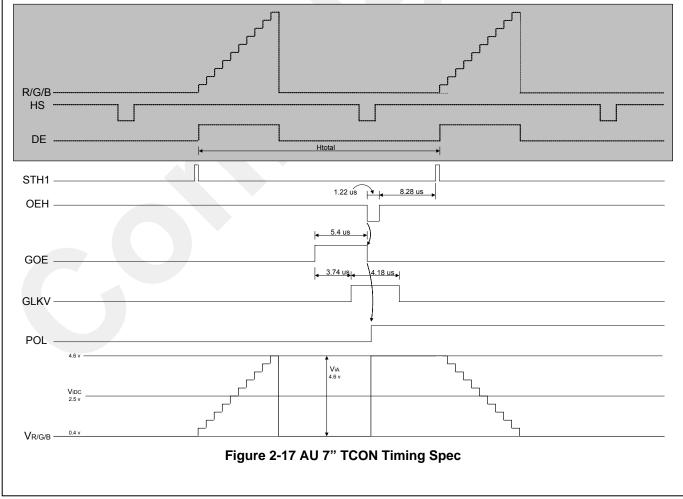

|         | IOW        | A4h, 00h;               | ; high byte of 2 <sup>nd</sup> row of Font[0], after this write, h/w will increase OSD  |